常见问答

- M051 系列(95)

- M0518 系列(97)

- M0519 系列(43)

- M0564 系列(1)

- Mini51 系列(90)

- Nano100 / 102 系列(101)

- Nano103 Base 系列(10)

- Nano110 / 112 LCD 系列(100)

- Nano120 USB 系列(111)

- Nano130 USB+LCD 系列(110)

- NUC029 系列(94)

- NUC100 / 200 系列(102)

- NUC120 / 122 / 123 / 220 USB 系列(116)

- NUC121/125 系列(1)

- NUC126 USB 系列(2)

- NUC130 / 230 CAN 系列(103)

- NUC131/NUC1311 CAN 系列(98)

- NUC140 / 240 USB+CAN 系列(114)

- M451 Base 系列(118)

- M451M 系列(117)

- M452 USB 系列(130)

- M4521 USB 系列(1)

- M453 CAN 系列(128)

- M463 CAN FD/USB HS 系列(1)

- M467 Ethernet/Crypto 系列(1)

- M471 系列(1)

- M479 Motor Control Series(1)

- M481 Base 系列(4)

- M482 USB FS OTG 系列(4)

- M483 CAN 系列(4)

- M484 USB HS OTG 系列(4)

- M485 Crypto 系列(4)

- M487 Ethernet 系列(4)

- M4TK 触摸 IC 系列(25)

- NUC442 / 472 系列(130)

- NUC472 Series(1)

- NUC505 系列(138)

常见问答

使用下列指令初始化系统时钟源时,为什么HCLK的时钟源无法切换成PLL? CLK->CLKSEL0 = (CLK->CLKSEL0 & ~CLK_CLKSEL0_HCLKSEL_Msk); CLK->CLKSEL0 |= CLK_CLKSEL0_HCLKSEL_PLL; 日期:2016-12-01

问:使用下列指令初始化系统时钟源时,为什么HCLK的时钟源无法切换成PLL?

CLK->CLKSEL0 = (CLK->CLKSEL0 & ~CLK_CLKSEL0_HCLKSEL_Msk);

CLK->CLKSEL0 |= CLK_CLKSEL0_HCLKSEL_PLL;

答:在执行第一行指令

CLK->CLKSEL0 = (CLK->CLKSEL0 & ~CLK_CLKSEL0_HCLKSEL_Msk);

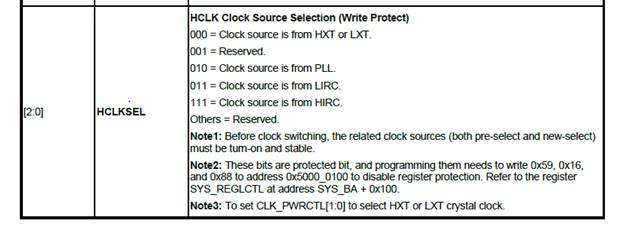

时,HCLKSEL (CLKSEL0[2:0])将设为0x00。当HCLKSEL设为0x00时,如下图所示,将切换HCLK的时钟源为外部晶振。

如果此时外部晶振没有稳定或使能,这时切换时钟源会失败,HCLKSEL将保持原本设定 (初始为0x07,时钟源为HIRC)。

因此在执行第二行指令

CLK->CLKSEL0 |= CLK_CLKSEL0_HCLKSEL_PLL;

时,HCLKSEL无法正确设为PLL,HCLK无法切换成PLL。

用户在切换时钟源时,需要确认要切换的时钟源已经稳定。建议使用以下方法切换时钟源:

1、直接写值

CLK->CLKSEL0 = (CLK->CLKSEL0 & ~CLK_CLKSEL0_HCLKSEL_Msk) | CLK_CLKSEL0_HCLKSEL_PLL;

2、调用函数

CLK_SetHCLK(CLK_CLKSEL0_HCLKSEL_PLL, CLK_CLKDIV_HCLK(2));

| 产品: | 微控制器 ,8 位 8051 微控制器 ,低管脚 8051 系列 ,标准 8051 系列 ,Arm Cortex-M0 微控制器 ,M051 系列 ,M0518 系列 ,M0519 系列 ,Mini51 系列 ,Nano100 / 102 系列 ,Nano103 Base 系列 ,Nano110 / 112 LCD 系列 ,Nano120 USB 系列 ,Nano130 USB+LCD 系列 ,NUC029 系列 ,NUC100 / 200 系列 ,NUC120 / 122 / 123 / 220 USB 系列 ,NUC130 / 230 CAN 系列 ,NUC131/NUC1311 CAN 系列 ,NUC140 / 240 USB+CAN 系列 ,Arm Cortex-M4 微控制器 ,M451 Base 系列 ,M451M 系列 ,M452 USB 系列 ,M453 CAN 系列 ,M4TK 触摸 IC 系列 ,NUC442 / 472 系列 ,NUC505 系列 |

|---|---|

| 应用: | |

| 功能: | Peripherals,ARM,Cortex-M0,Cortex-M4,Clock Control,HIRC,HXT,PLL |

粤公网安备 44030502010001号

粤公网安备 44030502010001号